SIS8300 µTCA for Physics Digitizer

10 Channel 125 MS/s 16-bit With Fast Feedback DACs

Development in co-operation with DESY under ZIM Förderkennzeichen 2460101MS9

The SIS8300 is a MTCA.4 (µTCA for Physics) digitizer card. High speed readout is implemented via a Virtex-5 FPGA based four lane PCI Express lane implementation.

Rear Transition Modules (RTMs) for different applications have been developed by different institutes and companies.

An overview can be found in the PDF of the 2011 Valencia NSS xTCA Workshop also.

Photograph

|

Central Design Parameters |

| Part Number | Xilinx FPGA | Memory |

|---|---|---|

| 04075 | XC5VLX50T-3FFG1136C | 4 x 1 GBit |

| 04364 | XC5VSX50T-3FFG1136C | 4 x 2 GBit |

| 05176 | XC5VLX85T-1/3FFG1136C | 4 x 2 GBit |

| tbd | XC5VLX110T-1/3FFG1136C | 5 x 2 GBit |

| SIS8300 Ordering Options | ||

| Name | Source | Description |

|---|---|---|

| SIS8900 | Struck | Single Ended Input Card |

| RTM7201 | HYTEC | 4-channel signal modulator |

| DWC8300 | Struck | Downconverter |

| BPM | DESY | Interleaved sampling for BPM readout |

| APD | DESY | Dual channel signal stretcher |

| Fast ADC RTM | SLAC | LLRF ADC Frontend |

| Available RTMs for SIS8300 | ||

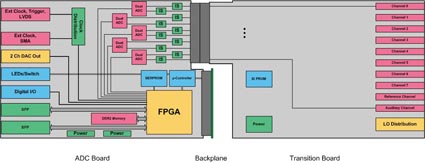

Block Diagram of SIS8300 With Downconverter Rear Transition Module